在学习和工作过程中,确实存在一种现象,那就是许多人在通信或软件工程领域,一旦实现了基本的功能,就认为万事大吉,任务完成了。他们很少深入研究信号的波形,或者深入思考信号与设计预期之间的差异。然后咱们再去改进、反馈这个过程。这种态度可能会限制个人和团队在技术深度和创新能力上的发展。它到底和我设计的有没有什么不一样,绝大多数人都没有,包括我也没有这个习惯,只不过是我看了一个聊关于开发的一个博主说的,我才意识到,这真的是一个值得讨论的问题。

别说在上板验证的时候已经写了testbanch去仿真了。仿真只是仿真,并非板子真正发出来的信号,一些物理因素造成的噪音,不去用示波器真正的查看,是很难去发现的。

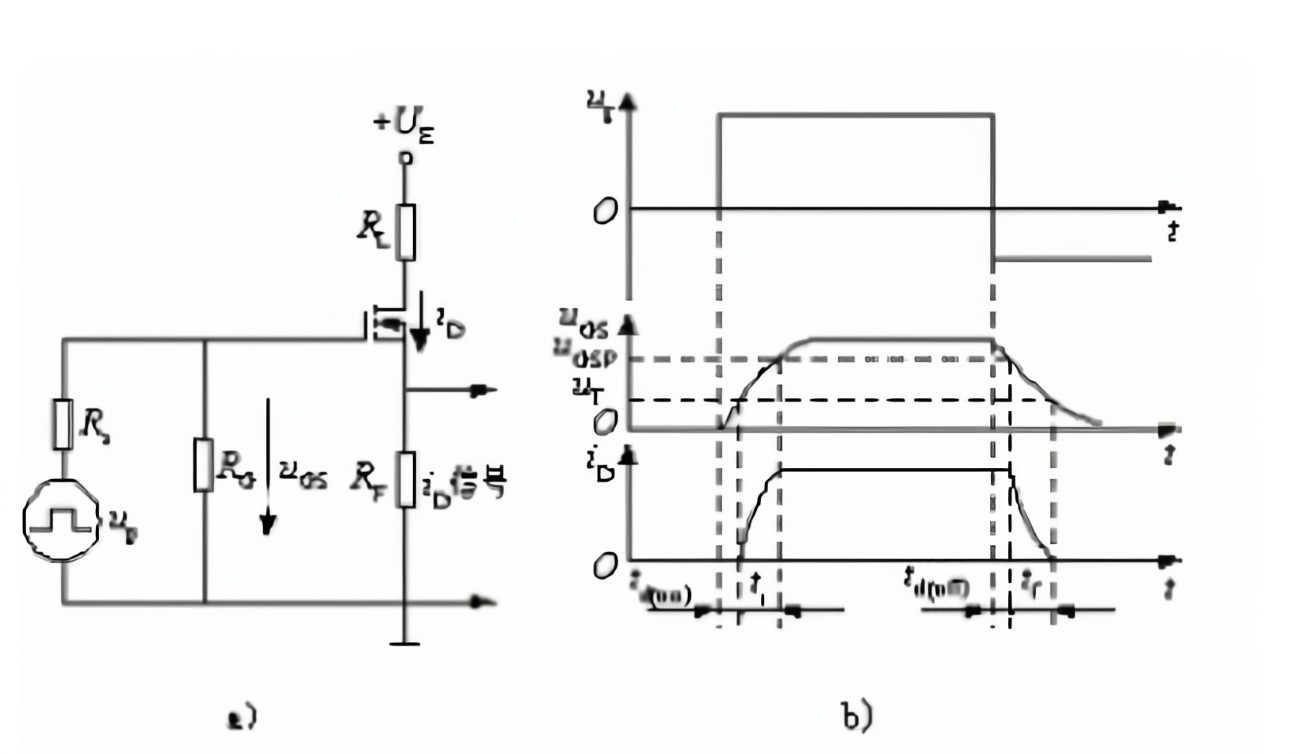

相信大家在学习数字电路知识的时候,或多或少会看到过电路动态特性的内容,书上也可能说:电路在物理世界中存在信号的传输存在时间延时,脉冲沿的基准时间定位在上升沿和下降沿的50%处。··· 传输延时时间$t_pLH$和$t_pHL$、脉冲宽度$t_w$等等。

例如我们在一个串口通信的时候,发送高电平的时候,拉高是需要时间的,而在仿真的时候,是发现不了这个问题的。即使发现了这个问题,大家可能也会联想到之前在数字电路知识的时候看到内容,脑海中依稀可以糊弄过去。

而这个问题同样可以衍生出:

- 为什么在拉高电平的时候是斜着的?

- 拉高的时间跟什么有关系?

- 怎么样削弱这段时间?

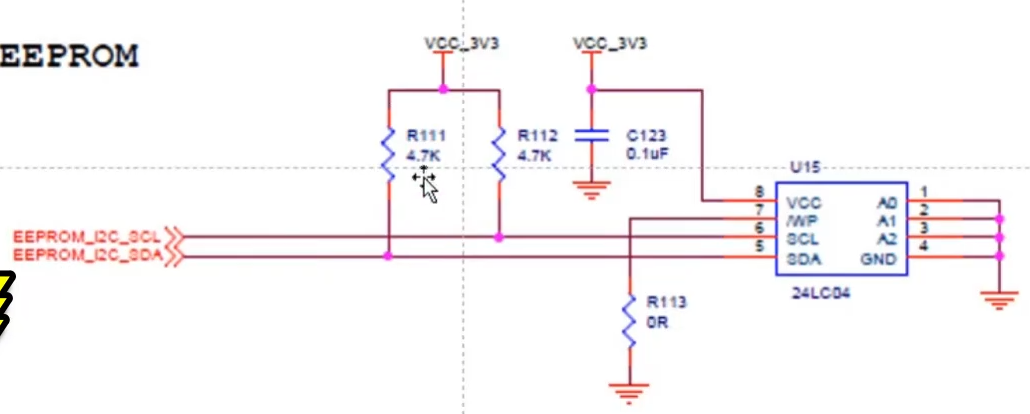

实际产生延时的原因:上拉电阻的大小,上拉电阻越大,延时越高