题目59_根据RTL图编写Verilog程序

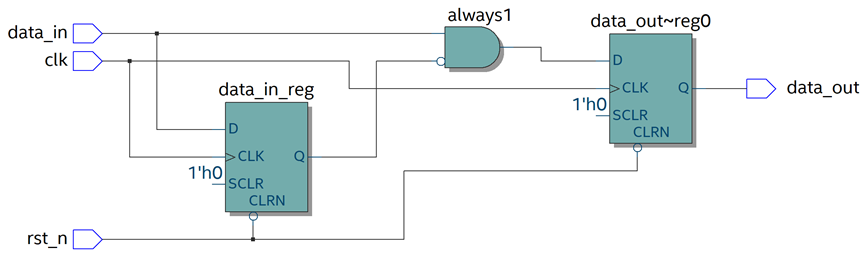

根据以下RTL图,使用 Verilog HDL语言编写代码,实现相同的功能,并编写testbench验证功能。

输入描述:

clk:系统时钟信号 rst_n:复位信号,低电平有效 data_in:输入信号

输出描述:

data_out:输出信号

题目解析

总体

题目本身不难,从我们的RTL视图中可以看到主要是由两个D触发器和非门和与门构成。复位信号使用低电平有效,

D触发器概念

D触发器(D Flip-Flop)是一种数字电路的常见的基本组件,主要用来存储一位二进制信息,并在时钟信号的控制下进行数据的存储和传输。

它在时钟信号的上升沿或者下降沿时,将输入端(D端)的数据锁存到输出端(Q端)

注意:Q端是正输出端,Q'端是反输出端(Q的反相)。在本题目中data_in_reg的Q端链接alway1的输入端时使用的就是Q'(反向输出端)

代码

`timescale 1ns/1ns

module RTL(

input clk,

input rst_n,

input data_in,

output reg data_out

);

reg Q;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

Q <=1'b0;

else

Q <= data_in;

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

data_out <= 1'b0;

else

data_out <= (data_in & ~Q);

end

endmodule

`