1.1 AXI4总线

- AXI4是ARM公司提出的一种高性能、高宽带、低延时的片内总线

- 主要描述了主设备和从设备之间的传输方式

- 分类:AXI4_FULL、AXI4_LIFE、AXI4_STREAM

- AXI4_LIFE,不支持突发传输,常用于数据量较小的传输,可以理解成轻量级的AXI4_FULL

- AXI4_FULL 也被称为AXI4,支持突发传输,突发长度为1~256,在只指定一次地址后,可以一次传输多大256个数据(数据的宽度取决于带宽)

- AXI4_STREAM 丢弃了地址项,常用于高速数据传输,因为没有了地址总线,所以用于数据流传送,允许无限制的数据突发传输规模

本次实验目的

- 通过使用DDR3中AXI4接口协议,完成DDR3的读写操作,参考b站野火,使用IP核实现

- 从零开始,通过时序图编写程序,完成DDR3的读写操作,参考为小白FPGA基础班

1.2 应用场景

- AXI4.0-lite主要用于内核和外设寄存器之间的通信。功能类似STM32中外设与CPU之间的通信时使用的协议,比如当访问串口的数据寄存器时,只访问四个字节的数据,所以使用AXI4.0-lite就特别合适。再比如,在PL写一个用于PS端操作的外设时,其外设寄存器一般通过AXI4.0-lite总线和PS交互。

- AXI4.0-full主要用于往DDR或者OCM中写入大量数据时使用。

- AXI_stream主要用于往FIFO等没有地址的数据缓冲区传送大量数据时使用。

关于每种协议详细的使用会在单独介绍中详细介绍,下面主要描述他们一致的地方。

1.3 常见名词解释

1.3.1 握手(handshake)是什么

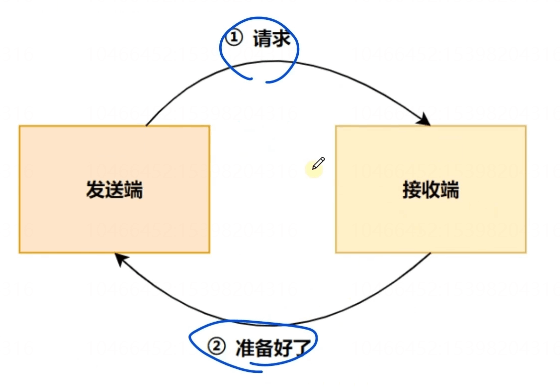

双向握手机制使用xxVALID和xxREADY信号线来控制,只有当xxVALID和xxREADY信号线都为高电平时,传输线上的信息才有效。发送端发起一个请求,接收端收到之后会回复一个信号,如果接收端没有发送信号,发送端会一直保持请求的状态,直到收到接收端回复的信号

主机如何将“写数据”写入到从机、

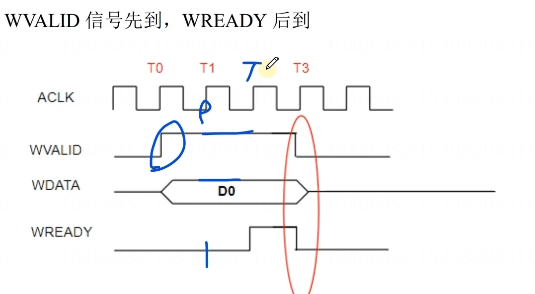

WVALID:主机写数据有效信号,方向:主机->从机

WDATA:主机写数据,方向:主机->从机

WREADY:表示从机是否准备好了 ,为高代表从机准备好了,方向:从机->主机

总结:只有当WVALID和WREADY信号同时为高时,数据才能被有效写入到从机,握手信号不仅仅发生在“写数据”、发送“写地址”等过程,只要主机和从机之间有数据交换,就会发送握手信号

1.3.2 什么是片内,什么是片外?

以下是我个人理解,没有经过验证,酌情查阅

片内On-Chip,指的是在FPGA内部系统,如AXI4协议在ZYNQ中PS端到PL端的传输,不涉及到外设的芯片

片外Off-Chip,与片内系统相反,需要借助外部芯片进行传输协议,例如我们的FPGA需要通过SPI协议与外部设备进行数据交换的时候,此时就是片外通信协议

1.3.3 什么是突发传输?

例如上面的图像,第一个时序是没有突发的,发送一次发送一个数据和一个地址进行对应,而下面的时序是具有突发传输的,主机发送4个字节,和首地址及末地址,不需要传输中间的地址,他的突发长度就是为4。还是比较好理解的

1.4 AXI4_LIFE通道介绍

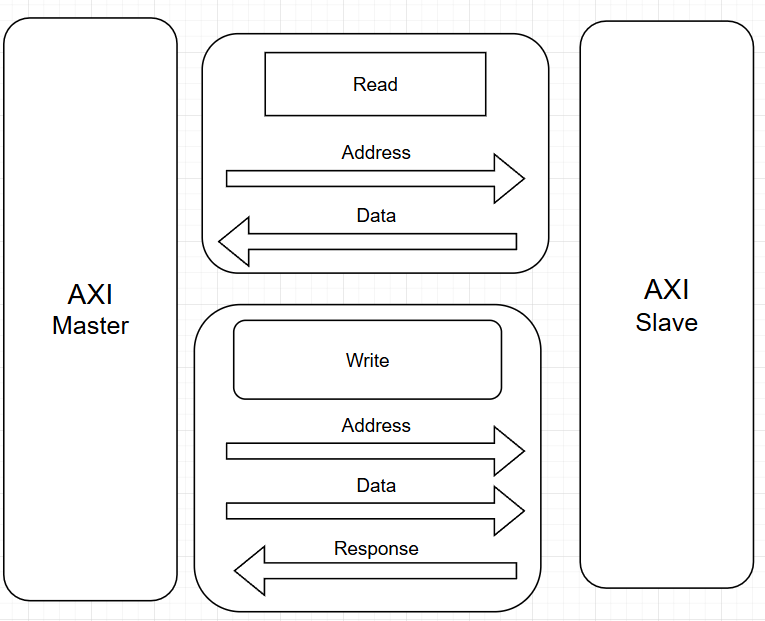

总结:读写分离,读的时候没有读响应通道

| 分类 | 信号定义 | 方向 | 功能 |

|---|---|---|---|

| 系统 | ACLK | 时钟 | |

| 系统 | ARESETN | 复位低有效 | |

| 写地址通道 | AWADDR | 主机 to 从机 | 写地址 |

| AWVALID0 | 主机 to 从机 | 写地址有效信号 | |

| AWREADY | 从机 to 主机 | 表示从机准备好了,可以接收写地址 | |

| AWPROT | 主机 to 从机 | 保护类型,表示一个传输的安全等级,默认为3’b000 | |

| 写数据通道 | WDATA | 主机 to 从机 | 写数据 |

| WVALID | 主机 to 从机 | 写数据有效 | |

| WREADY | 从机 to 主机 | 表示从机准备好了,可以接收写数据 | |

| WSTRB | 主机 to 从机 | 指示有效字节位置,类似于掩码 | |

| 写响应通道 | BRESP | 从机 to 主机 | 写响应 |

| BVALID | 从机 to 主机 | 写响应有效信号 | |

| BREADY | 主机 to 从机 | 表示主机准备好了,可以接收从机的响应 | |

| 读地址通道 | ARADDR | 主机 to 从机 | 读地址 |

| ARVALID | 主机 to 从机 | 读地址有效信号 | |

| ARREADY | 从机 to 主机 | 表示从机准备好了,可以接收读地址 | |

| ARPROT | 主机 to 从机 | 保护类型,表示一个传输的安全等级,默认为3’b000 | |

| 读数据通道 | RDATA | 从机 to 主机 | 读数据 |

| RVALID | 从机 to 主机 | 读有效 | |

| RREADY | 主机 to 从机 | 表示主机准备好了,可以接收从机的数据 | |

| RRESP | 从机 to 主机 | 读响应 |

1.5 写数据的模式

1、主机发送写地址和写数据的顺序关系:

主机可以先发送写地址,后发送写数据:

主机可以先发送写数据,后发送写地址:

主机可以同时发送写地址和写数据:

2、从机接收写地址和写数据的顺序关系:

从机可以先接收写地址,后接收写数据

从机可以先接收写数据,后接收写地址:

从机可以同时接收写地址和写数据:

我们常用的方式是主机同时发送写地址和写数据,从机同时接收写地址和写数据,然后发送写响应表示写的没问题

1.6读数据的模式

主机发送一个读地址 –> 从机接受读地址 –> 从机发送读数据和读响应

下一节,我们进行AXI4_Lite的读写通道和仿真代码的实现