开发中···锁存器和触发器的理解与整理.md

引言

大多数数字系统中,除了需要具有逻辑运算和算术运算功能的组合逻辑电路外,还需要具有存储功能的电路。组合电路与存储电路结合构成的时序逻辑电路,简称时序电路。这里讨论实现存储功能的两种逻辑单元电路:锁存器和触发器。

锁存器:用来存储状态信息,锁存器一般是电平触发,当锁存器使能时,输出随着输入变化,当没有使能时,输出一直为锁存器的状态信息

触发器:触发器当收到一个clk触发脉冲时,输出就会根据一定规则改变状态,然后保持直到下一个触发脉冲。

区别:锁存器和触发器的区别在与latch,当使能时,输入变化时输出就会跟随一起变化,没有clk,更容易产生毛刺。而flip-flop收到时钟的同步控制,只有clk触发时才会采样当前的输入。对脉冲电平敏感的是锁存器,对脉冲边沿敏感的是触发器。

寄存器:用来存储数据的小型存储区域,暂时存放参与运算的数据和运算结果,寄存器的存储电路是由锁存器和触发器构成的,因为1个锁存器或者触发器只能存储1位2进制数据,所以由N个锁存器或者触发器可以构成N位寄存器,在实际芯片中一般按照字节位数设计,所以一般与8位寄存器、16位寄存器。

下面我们着重分析一下锁存器和触发器原理并且举出简单的应用例子方便大家的理解与掌握。

1. 基本双稳态电路

双稳态电路

将两个非门进行交叉耦合的方式连接,则构成最基本的双稳态电路。从电路的逻辑关系可知,若Q=0,经过非门$G_2$ 反向得到$\overline{Q}$=1。

$\overline{Q}$反馈给$G_1$输入端,又保证了$Q$=0,由于两个非门首尾相接的逻辑锁定,因此电路能够自行保持在$Q$=0,而$\overline{Q}$=1的情况。

像这样的电路,具有0,1两种逻辑状态,一旦进入其中一种状态,就能长期保持不变的单元电路,称为双稳态存储电路,简称双稳态电路。

根据上面的分析,可以看出这个最基本的双稳态电路的功能极不完备。在接通电源后,它可能随机进入0或者1状态并且锁定在这个里面,我们无法控制和改变它的状态,从而并不能作为存储电路来使用。因此下面我们在这个最基本的双稳态电路下衍生出锁存器、触发器等功能完备的存储电路

2. SR锁存器

2.1 或非门构成SR锁存器

我们讲最基本的双稳态电路中的非门替换成或非门,则构成了上图所示的基本SR锁存器,它是一种具有最简单控制功能的双稳态电路,因为我们将非门替换了2输入一输出的或非门,那么留出的输入端也就成为了我们的输入控制端。

| $S_D$ | $R_D$ | Q | $\overline{Q}$ | 功能 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 保持 |

| 0 | 0 | 1 | 1 | 保持 |

| 0 | 1 | 0 | 0 | 置0 |

| 0 | 1 | 1 | 0 | 置0 |

| 1 | 0 | 1 | 1 | 置1 |

| 1 | 0 | 0 | 1 | 置1 |

| 1 | 1 | 0 | 0 | 不定 |

根据S、R的4种输入状态组合得到左表格,具体的分析过程请参考:电路技术基础-数字部分P232。

值得注意的是:在书中讲到S=R=1的时候,锁存器处在即非0也非1的非定义状态,为保证锁存器始终处于工作定义状态,输入信号应遵守$S_D$$R_D$约束条件,也就是死活不允许S=R=1。

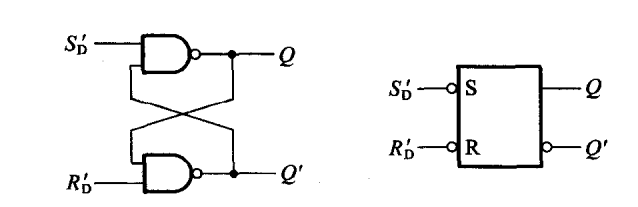

2.2 与非门构成SR锁存器

当然了,既然在最基本的双稳态电路中仅将非门替换成了或非门就构成了SR锁存器,同样也可以替换成与非门来构成另一种SR锁存器(也称:基本$\overline{S}$$\overline{R}$锁存器)。其原理都是一样的,只不过是其真值表有所出入罢了。

| $S_D{‘}$ | $R_D{‘}$ | Q | $\overline{Q}$ | 功能 |

|---|---|---|---|---|

| 0 | 0 | - | - | 不定 |

| 0 | 1 | 0 | 1 | 置1 |

| 0 | 1 | 1 | 1 | 置1 |

| 1 | 0 | 0 | 0 | 置0 |

| 1 | 0 | 1 | 0 | 置0 |

| 1 | 1 | 0 | 0 | 保持 |

| 1 | 1 | 1 | 1 | 保持 |

其约束条件同样遵守$S_D$$R_D$=0,

与非门是低电平有效,当输入SR=11时,就相当于我们最开始的最基本双稳态电路,起保持的功能

2.3基本SR锁存器的应用–硬件去抖动电路

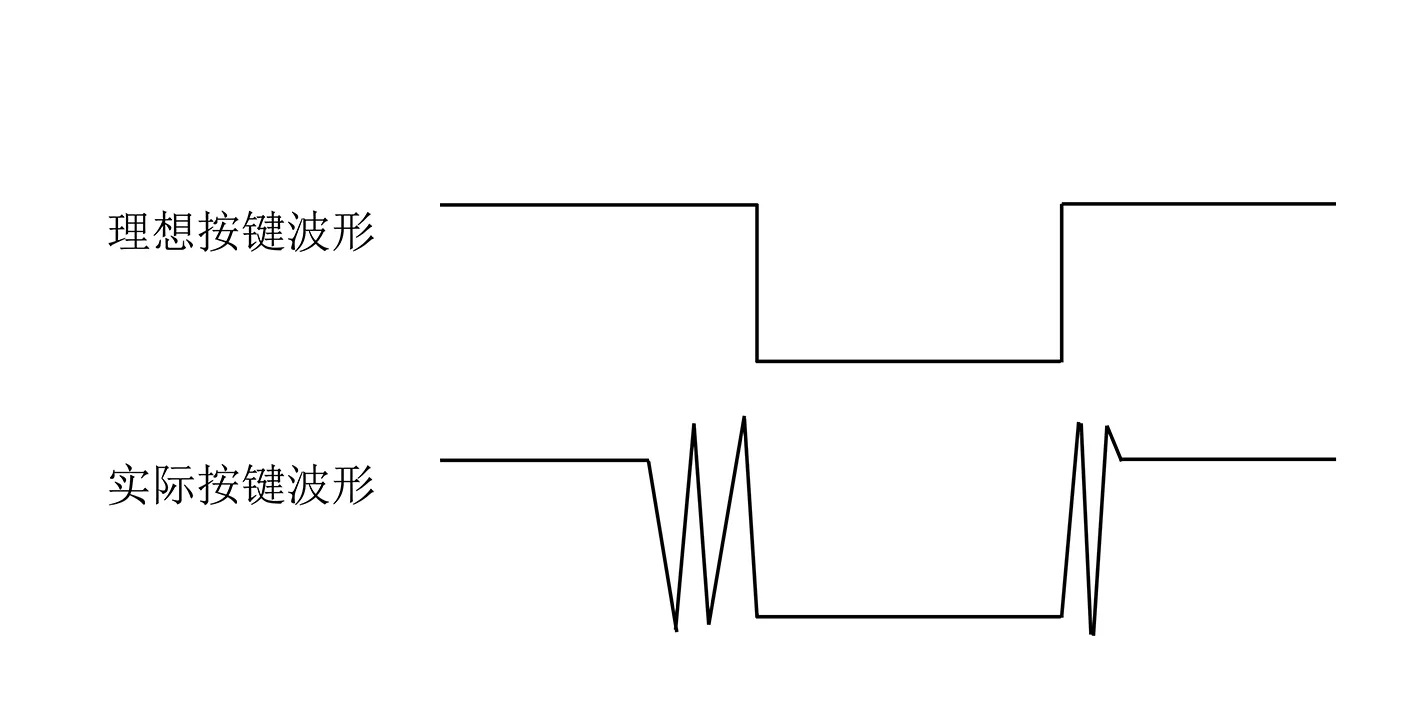

抖动如何产生?因为机械固有的物理特性,开关触点在瞬间接触的时候会有力学的回弹,使开关在“通”“断”之间反复横跳,造成 2-10 毫秒内信号不稳定。

在大部分情况下,这种信号抖动持续是没有影响的。但是当一个开关连接到一个足够“快”的电子设备上时,它可以检测到多次抖动并做出响应,那么就会引起问题。

在此,去除抖动的必要性就体现出来了。

2.3.1 原理

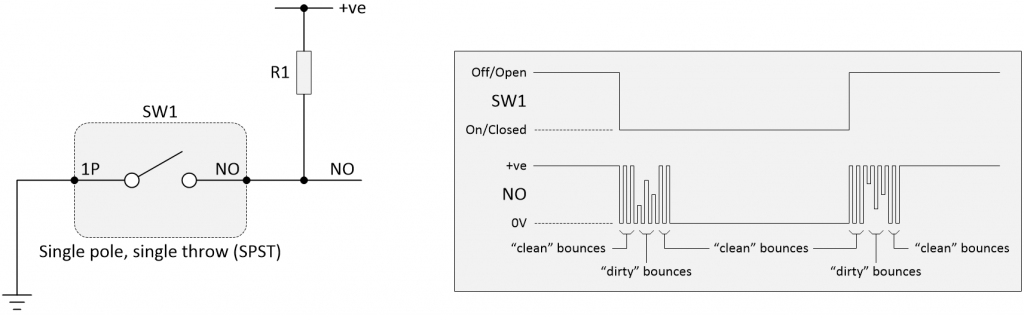

两种常见开关的抖动

下图是开关按下时,电平变化的示意图。

有时,电压在电源和地之间跃变;有时,则是在初始值和某个中间电压之间跳动。取决于不同开关的特性,这种跃变的行为也往往具有不确定性。

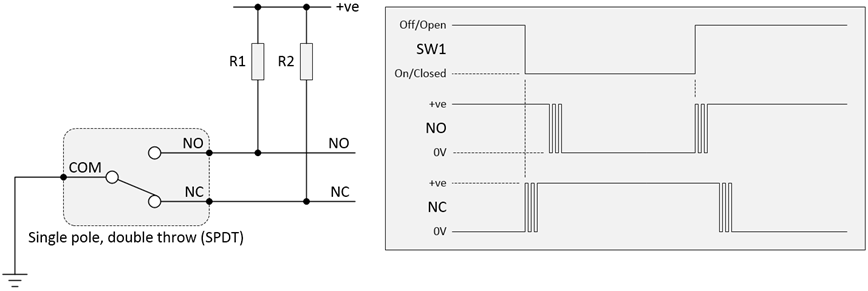

使用 SR 锁存器进行消抖

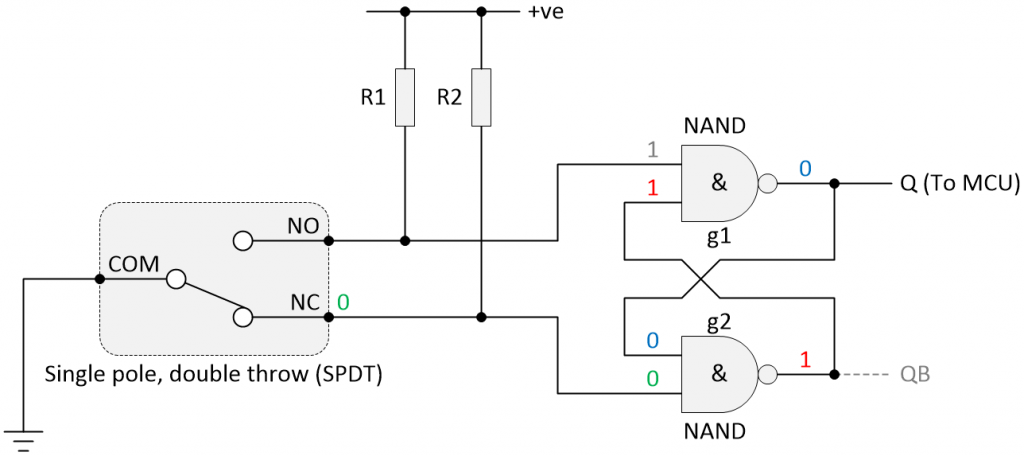

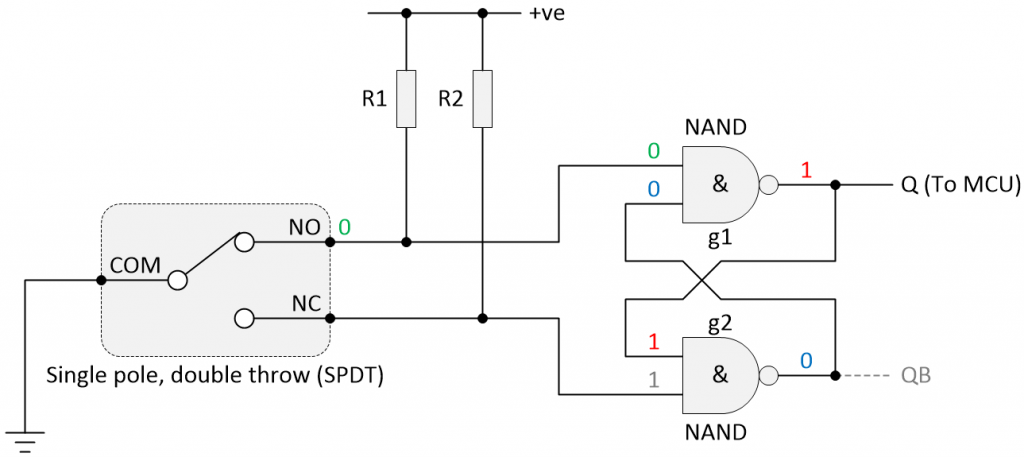

使用基于与非门的 SR 锁存器对 SPDT 开关进行消抖十分有效。下图是消抖电路的示意图。

以上图的“1”状态的情况为例,我们分析一下工作过程。

注意到,与非门构成的锁存器是低电平输入有效的。当开关未按下时,常闭触点 NO 接地,对于锁存器来说,此时 S 端为低电平,故 Q 被设为高电平。

当我们按下开关,触片就从 NO 断开而接触 NC。在接触 NC 的瞬间,有 S = 1(上拉), R = 0,故 Q 被设为低电平,完成电平转换。

但是前文提到,由于开关的弹性,在触片第一次接触 NC 后,还会弹起微小的距离,使得此时 NC 与触片断开。注意,由于弹起的距离很小,触片不足以碰到 NO,因此这时开关侧的 NO、NC 都处于“悬空状态”,对于锁存器来说,由于上拉电阻的存在,SR=11。

而根据锁存器的特性,当 S、R 同时为高电平时,输出端将保持原来的状态不变。

因此,在触片弹开而使得 NO、NC 悬空的一小段时间内,Q 端的输出并不受到影响,继续保持低电平,抖动就此消除。

方才分析的是触片反弹一次的情况,一般来说,触片在第一次接触 NC 后往往会反弹数次(振幅不断减小,直至于0),但通过刚才的分析,我们知道这无关紧要。在数次“悬空(实际是上拉)-拉低-悬空-拉低”的过程中,SR 锁存器不断“保持-置0-保持-置0”,Q 端的输出不会改变。

要想让 Q 端回到高电平,唯一的可能性就是松手,让触点接触 NO 端,把 S 端拉低。(嘿嘿,触片弹回 NO 的过程中也会反复横跳数次的。)

2.4 D锁存器

与SR锁存器不同,D锁存器在工作中不存在非定义状态,因而得到广泛的应用。目前,CMOS集成电路主要采用传输门控D锁存器和逻辑门控D锁存器两种电路结构形式,特别是前者电路结构简单,在芯片中占用的面积小而更收青睐。

(这里占个坑位,后面再讲)

3. 触发器

这是一种对脉冲边沿敏感的双稳态电路,只对时钟信号的上升沿或者下降沿敏感,而在其它时刻保持不变,例如我们熟知的计数器、移位寄存器。这种对脉冲边沿敏感的状态更新称为触发,具有触发工作特性的存储单元称为触发器,根据触发边沿不同可以分为:上升沿触发和下降沿触发。

目前应用的触发器主要与三种电路结构:主从触发器、维持阻塞触发器和利用传输延迟的触发器。其中主从结构的D触发器在芯片上占用的面积最小,逻辑设计也简单从而广泛使用

(这里占个坑位,后面再讲)