1. 上板验证

··· 关于上板,需要搁置一段落,我看的野火教程并没有更新到上板验证的部分,所以需要去观看其他相关的实操视频来填坑~~

2. 理论学习

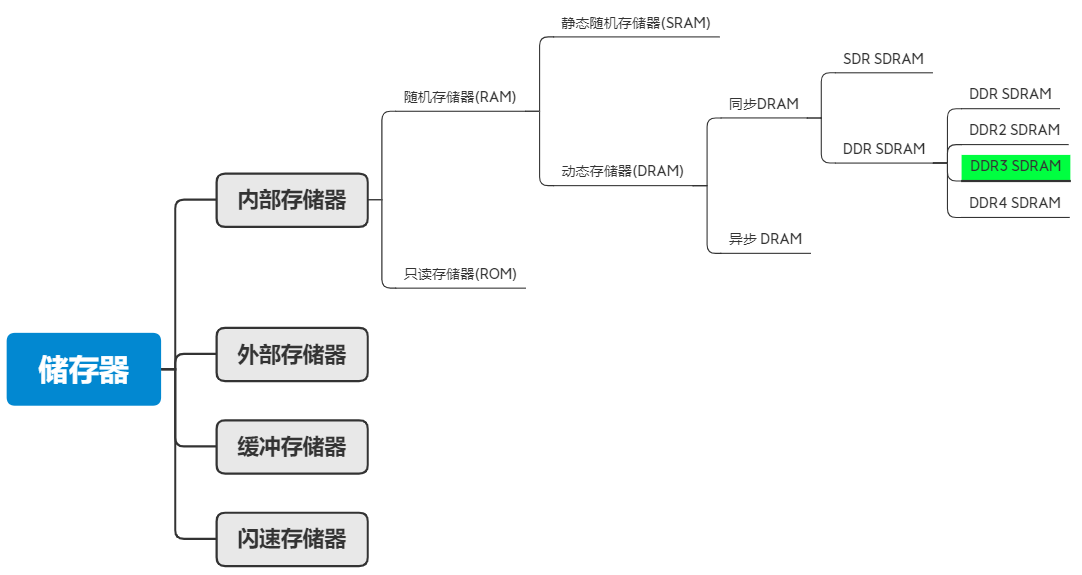

2.1 DDR3 SDRAM的基本概念

DDR3内存条就像一本由多个页面组成的书。在这本书中,每一页都代表内存中的一个逻辑单元,也就是一个bank。每个bank是内存的一个独立部分,可以独立地进行数据的读写操作。

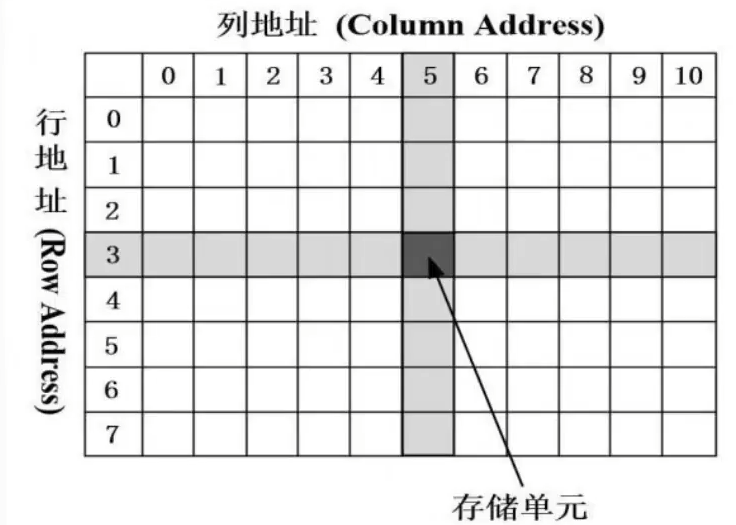

在每一页(bank)中,数据被组织成行和列,类似于表格。通过行地址和列地址,我们可以定位到这个表格中的一个特定单元格,这个单元格就是内存中的基本逻辑单元。这个单元格可以存储一个字(word),其大小由DDR3内存条的位宽决定。例如,如果内存条的位宽是64位,那么这个字就可以存储64位二进制数据。

位宽是内存条的一个重要参数,它决定了内存一次能够传输的数据量。位宽越大,单次传输的数据量就越多,从而提高内存的带宽和性能。

内存的总容量是由所有bank的容量总和决定的。每个bank的容量乘以bank的数量,再乘以每个存储单元的位数,就得到了整个内存条的总容量。因此,内存条的容量可以通过增加bank的数量或增加每个bank的容量来提升。

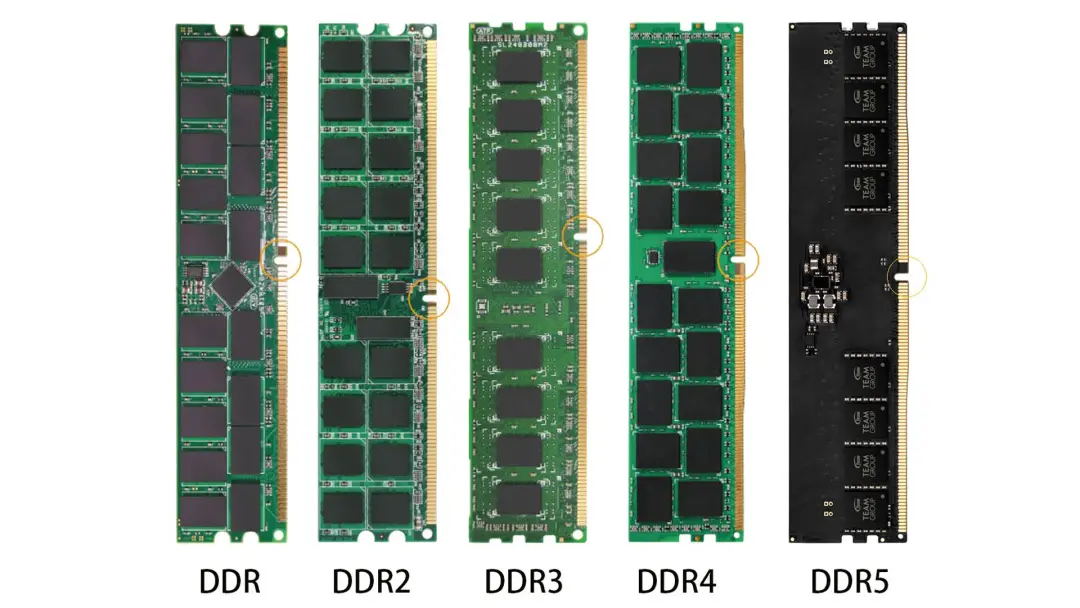

DDR3 SDRAM英文全称“Double-Data-Rate- Three Synchronous Dynamic Random Access Memory”,翻译成中文为“第三代双倍速率同步动态随机存取内存”或“同步动态随机存储器”,是动态随机存储器(简称:DRAM)家族的一份子。

关键词:双倍率、同步、动态、随机

双倍速率:它可以在时钟的上升沿和下降沿都可以传输一个数据

同步:通常DRAM是异步的,而DDR3是同步的,所谓的同步,就是说它的一个数据在读取的时候 或者说是在写入的时候是按时钟同步的

动态:DDR3是一个数据存储器,它是使用电容对数据进行一个存储,主要是因为电容一个特性可以存储电荷。但是电容存储的电荷会慢慢的进行一个释放,这个时候就会造成数据的一个不确定性,可能读取的数据时错的,这个时候,我们的DDR3就会进行一个不断地刷新,也就是不断地给他进行充电,来保证这个存储阵列内部的数据可靠性

随机:数据在DDR3当中,并不是按照线性依次存储的,而是自由的指定地址进行数据的读写。只要给它一个地址,它就可以根据这个地址找到具体的一个存储单元,然后就可以对这个地址进行数据的一个读写操作

除此之外,它的可见存储量也非常大、读取数据快以及价格相对便宜的特点

当然,它也有缺点,

- 因为是动态,那么我们就要不断的对它进行充电和放电

- 因为数据读取时是随机读取的,需要地址,它的行和列地址是共用了一个地址端口,使用了一个分时复用的方式

这两个缺点就使得DDR3,对操作时序的要求比较严格,进而导致控制逻辑十分复杂。但是例如Xilinx提供了DDR的IP核可以进行调用

2.2 DDR3 SDRAM数据存取原理

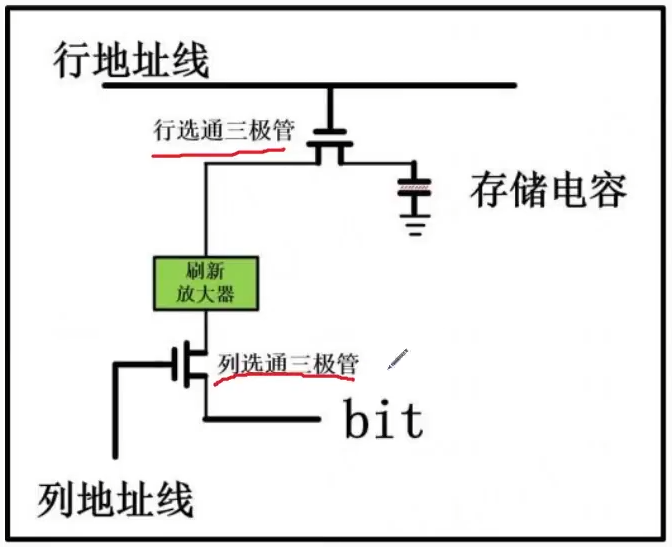

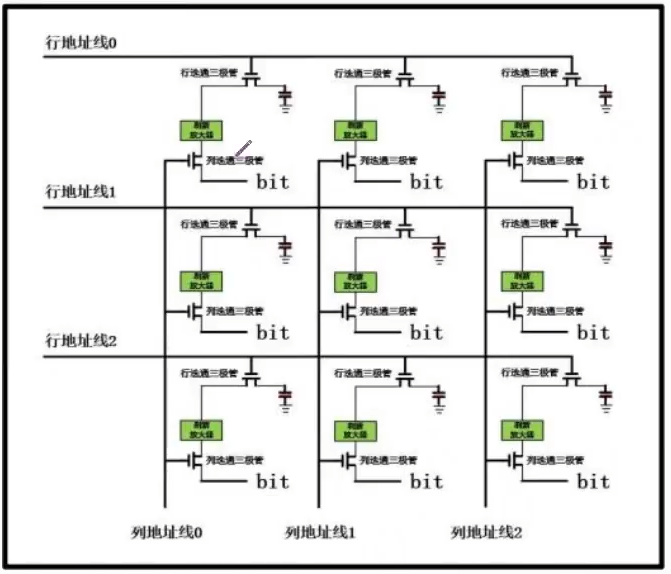

简单来说,DDR3内部可以理解为一个存储阵列,这就是DDR区别于管道式存储实现随机地址存储的一个结构特点。上图中。每一个表格相当于一个存储单元,存储阵列也叫做逻辑Bank也可以叫做L-Bank,一个DDR3一般有8个Bank,这些Bank就构成了整体的一个存储空间。如果要想实现在DDR3中某一个存储单元进行一个读写数据操作,我们首先需要确定它的一个Bank地址,然后通过一个行地址和一个列地址(满足一个先行后列的要求)

DDR3的存储:Bank –> RC(行列) –> 存储单元

总存储容量(Bit)= bank数量 X 行数量 X 列数量 X 存储单元容量

一个存储单元又可以划分为若干个比特(根据DDR3的位宽来决定),如果说我们的DDR3是16位的,那么一个存储单元中就可以存储16个比特数据、每一个比特是存储在单独的存储体当中,存储体是利用电容能够保持电荷以及充放点的一个特性制成的

DDR3数据手册下载地址

MT41K128M16JT:https://cdn.jsdelivr.net/gh/zikwq/Blog_Pic/MT41K128M16JT.pdf

4Gb_DDR3L:https://cdn.jsdelivr.net/gh/zikwq/Blog_Pic/4Gb_DDR3L.pdf

2.3 DDR3 SDRAM器件引脚说明

注意,此处引脚说明并非实例化时所使用的引脚,而是器件的x16 Ball Descriptions引脚说明,是总DataSheet中翻译过来的。****

| 引脚 | 位宽 | 端口类型 | 功能描述 |

|---|---|---|---|

| CLK,CLK# | 2Bit | Input | 差分时钟:DDR3 SDRAM由差分时钟驱动,所有DDR3 SDRAM输入信号都在时钟上升沿和下降采同时CLK还递增内部突发计数器并控制输出寄存器。 |

| RESET# | 1Bit | Input | 芯片复位信号,低电平有效 |

| CKE | 1Bit | Input | 时钟使能:屏藏时钟,冻结当前操作,高电平有效,信号有效时,所有信号才能被正确送入DDR3 SDRAM. |

| CS#(CS_N) | 1Bit | Input | 片选信号:屏蔽和使能所有输入输出端口,CLK、CKE、DQV除外,低电平有效。为高电平时,屏蔽所有命令,但已经突发的读/写操作不受影响。 |

| CAS#(ACS_N) | 1Bit | Input | 列选通信号:低电平有效,为低电平时,A[9:0]输入的为列地址 |

| RAS#(RCS_N) | 1Bit | Input | 行选通信号:低电平有效,为低电平时,A[13:0]输入的为行地址 |

| WES#(WE N) | 1Bit | Input | 写使能信号,低电平有效,为低电平时,使能写操作和预充电。(CS#、CAS#、RAS#、WE#)构成DDR3 SDRAM操作命令。 |

| LDM,UDM | 1Bit | Input | 数据掩码:LDM低字节掩码,UDM高字节掩码,若LDM信号为高电平,在下一个时钟周期的时钟上升沿,输出数据总线的低字节为高阻态。UDM则相反。 |

| ODT | 1Bit | Input | 片上终端使能,若为高电平,可以消除DQ、DQS、DW信号的反射。 |

| BA[2:0] | 1Bit | Input | L-Bank地址:选择不同的逻辑Bank进行相关数 |

| A[14:0] | 15Bit | Input | 行列地址总线:提供模式寄存器配置期问的操作码。 |

| DQ[15:0] | 16Bit | Inout | 数据总线 |

这里只列出来一部分端口,需要完整的内容可以去上面的芯片手册中获取更加完整的内容!

2.4 DDR3 时钟分析

系统时钟:MIG IP核的工作时钟,一般命名为sys_clk

参考时钟: MIG IP的参考时钟,必须为200MHZ,命名位ref_clk

DDR3芯片的工作时钟:由FPGA输入到DDR3芯片,为差分时钟

用户端时钟:MIG IP核输出给用户端的时钟,命名为ui_clk

在DDR3芯片工作的时钟与用户端时钟有一个比例关系:

DDR3芯片的工作频率:用户端时钟频率为4:1或者2:1,当DDR3芯片的工作时钟为800MHZ的时候,比例只能是2:1。

2.5 DDR3的模块实验

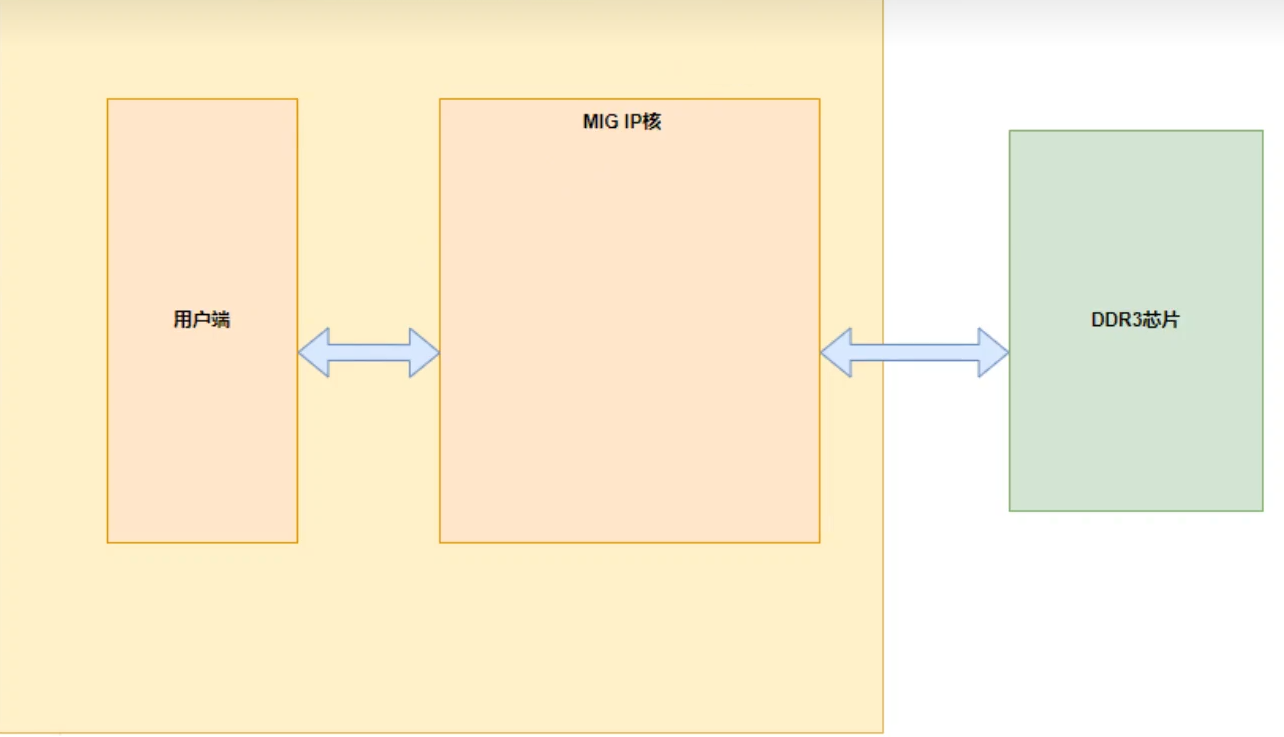

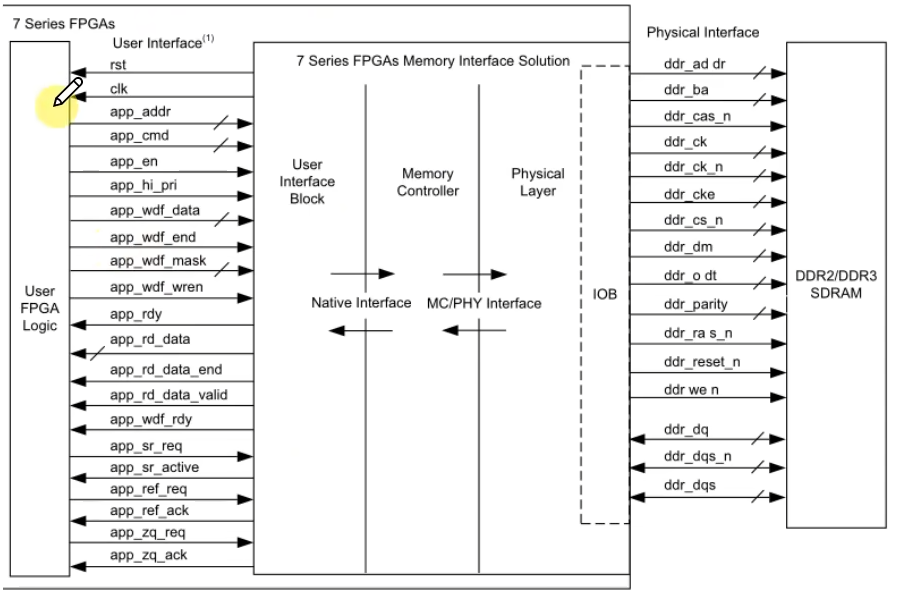

用户端接口与两种:Native接口和AXI4接口,接下来我们使用AXI4接口进行实验

实验目标:我们通过MIG IP核对DDR3写入1024个数据,然后进行读取出来的实验,并使用ila在线逻辑分析仪,对数据进行抓取

从我们的原理图中可以看到,我们在PL端使用的ddr3型号是MT41K256M16RE-125。

通过前面的讲解介绍,DDR3的存储容量4Gb的存储容量。图中可以看出来,我们PL端是并联了2片DDR3,PL 端 2 片内存组成 32bit 数据接口,也就是4Gb的存储容量=1GB内存大小 ,

2.5.1 模块框图绘制

在上面的框图中,我们的axi_ddr_top还需要实例化四个模块,分别是:读写控制模块、读模块、写模块、还有MIG IP核。下面进行我们mig ip核的配置

2.5.2 MIG DDR IP核配置

- 点击后在右边搜索栏目搜索“MIG”,直接双击打开,这里显示的是我们fpga 工程的相关信息,点击下一步

- 基本信息的配置

- 引脚信息

这里是是否兼容其他的芯片选项,我们这里就不用管

- 控制器的选择

- 控制器的基本配置

关于这边的时钟,如果我们是K7的板子,DDR3工作时钟是可以达到800MHZ的,下面的 用户端时钟只能必须为200MHZ,如果是A7 的板子,他的工作时钟通常为最高为600MHZ

- AXI总线的配置

- 内存设置–对应的阻抗可以在数据手册中搜索:“output drive strength”

- FPGA选项

- 引脚选择

到这里都已经完成了,后面就是正常默认完成就行

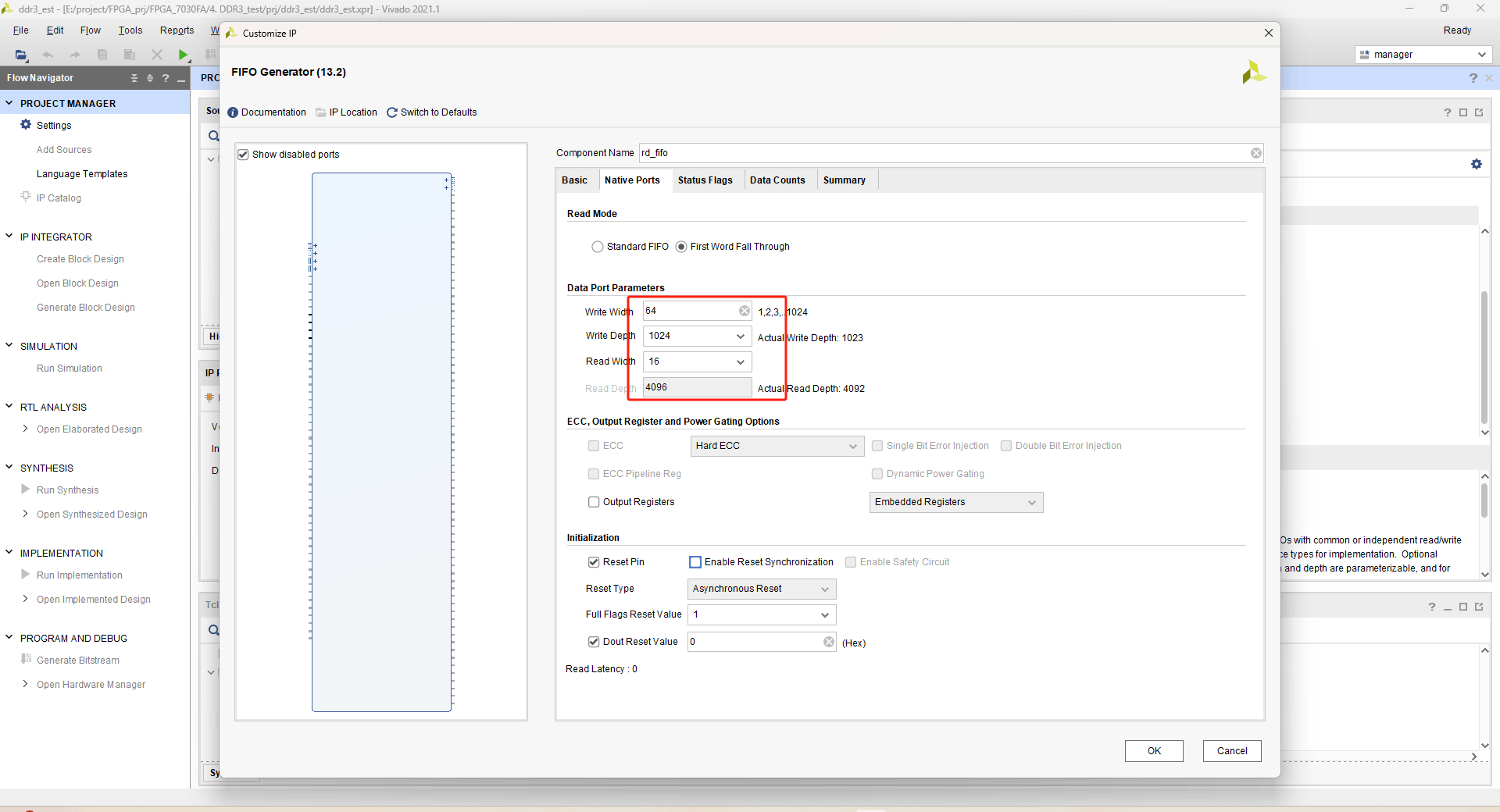

2.5.3 声明两个FIFO IP核

- 打开我们的ip核目录,在搜索框里面搜索FIFO

- 配置基本信息

- 配置常规接口

- 配置标志信号

- 配置数据计数器

下面是读FIFO的配置,跟写FIFO类似只有下面一张图的配置跟写FIFO不一样

2.5.4 PLL锁相环IP核配置

- 打开目标锁相环

- 配置输入输出时钟,这里我们输入是100MHZ,输出320MHZ的DDR3工作时钟

2.5.6 RTL视图

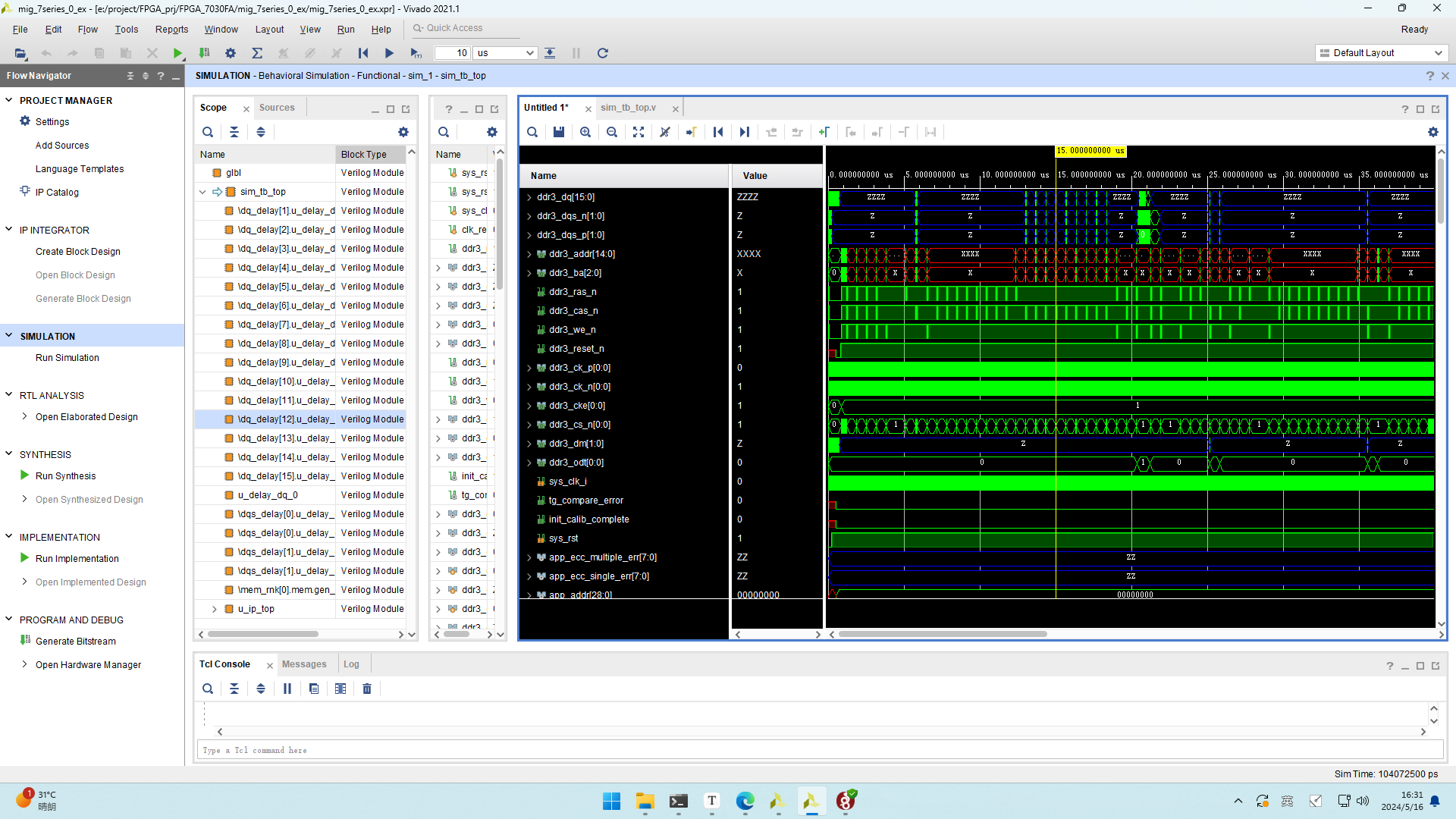

2.5.7 仿真MIG IP核

2.5.8 上板验证——ILA仿真

在我们需要抓取的信号前面加上

(*mark_debug="true"*)3. Native接口概述

4. AXI接口概述

AXI总线你需要知道的事儿 - 知乎 (zhihu.com)

AXI的英文全称“Advancede Xtensible Interface” ,即为高级可扩展接口,他是ARM公司所提出的AMBA协议(高级微控制器总线框架协议,包含了四种不同的总线标准:AHB、ASB、APB、AXI)的一部分

之所以要采用AXI4接口对DDR进行读写是因为Xilinx的MIG DDR IP核,无论是6系列还是7系列还是最新的FPGA,都集成了AXI4接口,采用AXI4接口进行读写,后续可以兼容Xilinx的其他FPGA,可复用性更强。

2.5.1 AXI接口的特点

AXI协议是一种高性能、高宽带、低延时的片内总线,有如下特点:

- 总线地址/控制和数据通道是分离的;它可以分为五个不同的通道:写地址通道、写数据通道、写响应通道、读地址通道、读数据通道

- 支持不对其的传输;

- 支持突发传输,突发传输过程中只需要首地址;突发长度Burst Length一般为8

- 具有分离的读写数据通道;

- 支持显著传输访问和乱序访问;

- 更容易进行时序收敛;

2.5.2 AXI接口分类

AXI4协议支持有三种类型的接口,分别是:

- AXI4:高性能的存储映射接口

- AXI4_Lite:用于数据量少的存储映射通信

- AXI4_Stream:高数据流的一个传输,非存储映射接口。就像一个FIFO一样,不需要地址,直接连续的一个读写数据,主要用于视频、高速的一个AD、PCIE、DMA接口等需要高速数据传输的一个场合

2.5.3 什么是存储映射

当一个协议是存储映射的时候,主机对从机进行读写操作的时候,会标明一个地址,这个地址就对应系统存储空间当中的一个地址,就表示针对该存储空间进行一次读写操作。

主要用于处理器访问处理器等,需要指定地址的一个高速数据传输的一个场景。

存储器映射是硬件抽象的一种形式,它允许软件通过统一的内存模型来与硬件设备交互,这在现代计算机系统中非常常见。在AXI4协议中,存储映射的概念被用来实现高效的系统内通信,允许不同的处理器和外设通过共享的地址空间进行数据交换和控制。除了存储映射外,还有寄存器映射,详情请参考上面这篇参考博客。

2.5.4 AXI时序

AXI时序数据手册下载地址: